Table of Contents

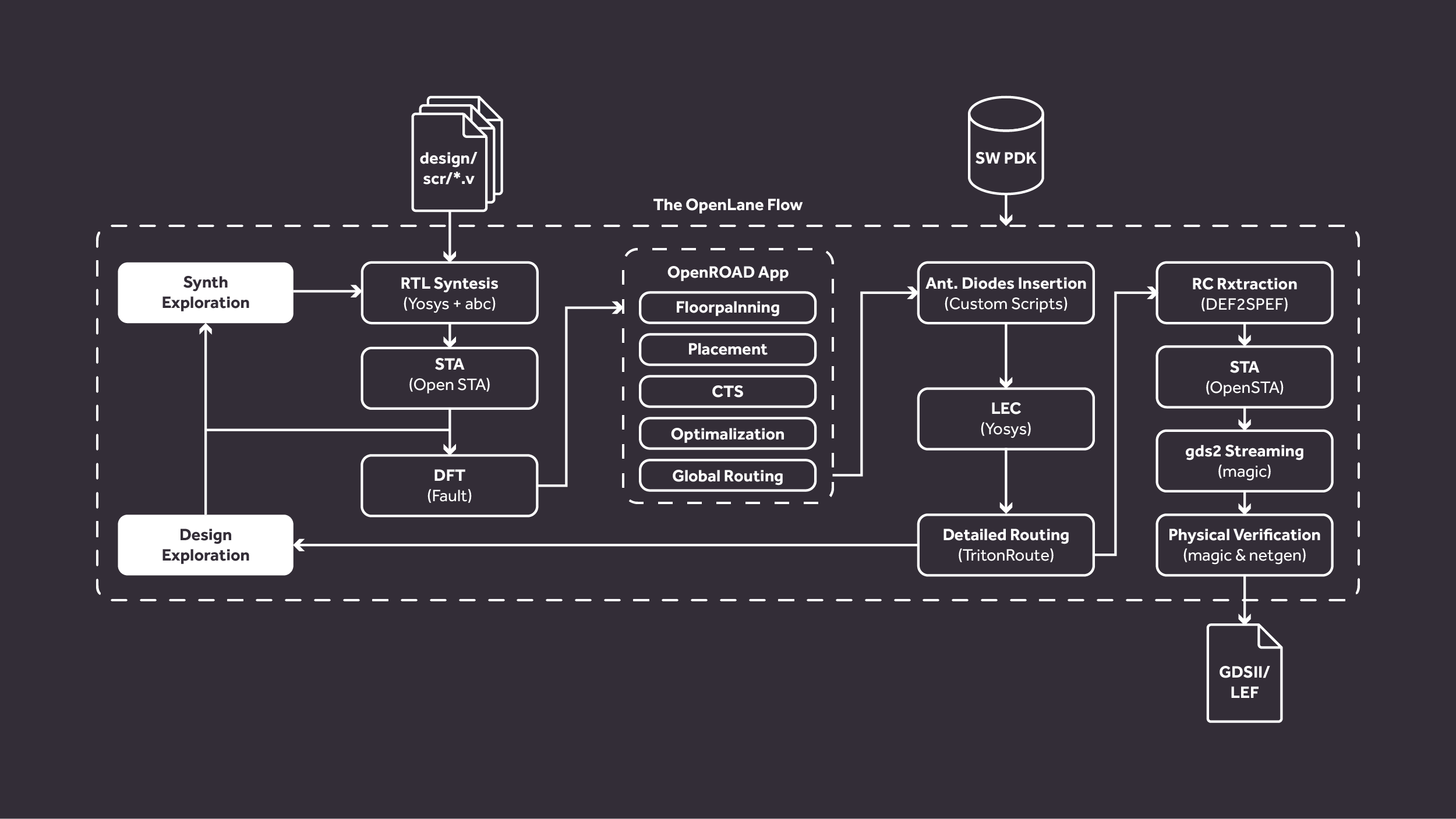

OpenLANE is a completely automated RTL to GDSII flow which embeds in it different opensource tools, namely, OpenROAD, Yosys, ABC, Magic etc., apart from many custom methodology scripts for design exploration and optimization. Openlane is built around Skywater 130nm process node and is capable of performing full ASIC implementation steps from RTL all the way down to GDSII. The flow-chart below gives a better picture of openlane flow as a whole.

Image Coutersy: Chips Alliance

Place and Route (PnR) is the core of any ASIC implementation and Openlane flow integrates into it several key open source tools which perform each of the respective stages of PnR. Below are the stages and the respective tools that are called by openlane for the functionalities as described:

- Synthesis

yosys/abc- Perform RTL synthesis and technology mapping.OpenSTA- Performs static timing analysis on the resulting netlist to generate timing reports

- Floorplaning

init_fp- Defines the core area for the macro as well as the rows (used for placement) and the tracks (used for routing)ioplacer- Places the macro input and output portspdngen- Generates the power distribution networktapcell- Inserts welltap and decap cells in the floorplan

- Placement

RePLace- Performs global placementResizer- Performs optional optimizations on the designOpenDP- Performs detailed placement to legalize the globally placed components

- CTS

TritonCTS- Synthesizes the clock distribution network (the clock tree)

- Routing

FastRoute- Performs global routing to generate a guide file for the detailed routerTritonRoute- Performs detailed routingOpenRCX- Performs SPEF extraction

- Tapeout

Magic- Streams out the final GDSII layout file from the routed defKLayout- Streams out the final GDSII layout file from the routed def as a back-up

- Signoff

Magic- Performs DRC Checks & Antenna ChecksKLayout- Performs DRC ChecksNetgen- Performs LVS ChecksCVC- Performs Circuit Validity Checks

Follow this link for brief overview on OpenLane and its installation: Openlane docs

Library Exchange Format (LEF) file serves the purpose of protecting intellectual property and is basically of two types:

-

Cell LEF - It's an abstract view of the cell and only gives information about PR boundary, pin position and metal layer information of the cell, information necessary for PnR tool to correctly place and route a block.

-

Technology LEF - It contains information about available metal layer, via information, DRCs of particular technology used by placer and router etc.. The below diagram highlights the difference between a layout and a LEF (Image Courtesy: Google):

The goal of this project is to design a single height standard cell and plug this custom cell into a more complex design and perform its PnR in the Openlane Flow.The standard cell chosen is CMOS inverter and the design into which it is plugged is prebuilt femtoRV32 core.

FemtoRV is a minimalistic RISC-V design, with easy-to-read Verilog sources directly written from the RISC-V specification. The most elementary version (quark), an RV32I core, weights 400 lines of VERILOG (documented version), and 100 lines if you remove the comments. We will be using quark version for our custom layout.

List of issues we faced while sythesizing the available code: Challenges

- Follow this blog for magic vlsi + skywater-pdk local installation guide

- Or magic can also be invoked in pdks folder of Openlane installation directory:

/OpenLane/pdks/sky130A/libs.tech/magic

Under this directory runmagic -T sky130A.tech &

We will be creating designs in single height standard cell format, so the dimensions needs to be multiple of the single height which for sky130 has a nomenclature of unithd with dimensions 0.46 x 2.72 (w x h) for sky130_fd_sc_hd PDK variant. Thus, step 1 is to create a bounding box of width 1.38 x 2.72 (3w x h).

- Not sure why this isn't working for me but we will see later, in magic tkcon window:

property FIXED_BBOX {0 0 138 272}

- Followed by designing the inverter in magic, and making sure there are no DRC errors

Note:

the layout is included in the repo can be viewed in magic layout window as magic -T sky130A.tech inv.mag &

Once the layout is ready, the next step is extracting the LEF file for the cell. However, certain properties and definitions need to be set to the pins of the cell which aid the placer and router tool. For LEF files, a cell that contains ports is written as a macro cell, and the ports are the declared PINs of the macro. Our objective is to extract LEF from a given layout (here of a simple CMOS inverter) in standard format. Defining port and setting correct class and use attributes to each port is the first step. The easiest way to define a port is through Magic Layout window and following are the steps:

- In Magic Layout window, first source the .mag file for the design. Then

Edit >> Textwhich opens up a dialogue box.

- For each layer, make a box on that particular layer and input a label name along with a sticky label of the layer name with which the port needs to be associated, ensure the port enable checkbox box is checked and default checkbox is unchecked as shown below:

Above two figures, port A ( in port ) and port Y ( out port ) are taken from the locali ( local interconnect ) layer.

Note: The number mentioned in the text area next to the enable checkbox defines the order in which the ports will be written in LEF file.

For power and ground layer, can be done in same or different layer. Here, we have connected gnd and power are taken from metal 1 ( notice the text area beside sticky checkbox )

Once the port definition is done, the next step is to set port class and port use attributes. The "class" and "use" properties of the port have no internal meaning to magic but are used by the LEF and DEF format read and write routines, and match the LEF/DEF CLASS and USE properties for macro cell pins.

Certain properties need to be set before writing the LEF. There are specific property names associated with the LEF format. Once the properties are set, lef write command write the LEF file with the same nomenclature as that of the magic layout file.

Run the following commands in magic tkcon window to extract spice file:

extract all

ext2spice cthresh 0 rthresh 0

ext2spice

In order to simulate the spice file necessary libraries and simulation source code is included, and model names are modified to given MOSFET definitions within the library.

Simulation results:

In order to include the new standard cell in the synthesis, copy the sky130_vsdinv.lef file to the designs/femto/src directory

Since abc maps the standard cell to a library abc there must be a library that defines the CMOS inverter. The sky130_fd_sc_hd__typical.lib file from link to be copied to the designs/femto/src directory (Note: the slow and fast library files may also be copied and modified according to custom cell design).

Open OpenLane Directory and enter:

make mountList of commands:

./flow.tcl -design femto -init_design_config -add_to_designs

./flow.tcl -design femtoThe first step in synthesis is determining the optimal synthesis strategy SYNTH_STRATEGY for your design. For that purpose there is a flag in the flow.tcl script, -synth_explore that runs a synthesis strategy exploration and reports the results in a table in a html file under femto/reports/.

./flow.tcl -design design_name -synth_explore./flow.tcl -interactiveLoad the package file

package require openlane

0.9Note 1: Now run the commands in the following sequence and ensure no steps are skipped

prep -design femto -tag full_guideInclude the below command to include the additional lef (inv.lef) into the flow:

set lefs [glob $::env(DESIGN_DIR)/src/*.lef]

add_lefs -src $lefs

run_synthesisA "runs" folder is created under femto folder

Since we have used a -tag name to be full_guide, a folder with tag_name is created, if tag name is not mentioned a folder titled "today_date..." will be the directory under femto

presynthesis

post-synthesis

Calculation of Flop ratio

Flop ratio = Number of D Flip flops

______________________

Total Number of cells

dfxtp_4 = 1178,

Number of cells = 6709,

Flop ratio = 1178/6709 = 0.1755 = 17.55%

The objective is to design the layout of silicon area and establish a reliable power distribution network (PDN) for powering the various components of the synthesized netlist. Prior to placement, it is essential to determine the macro placement and blockages to ensure a compliant GDS file.

To achieve this, a ring is created that connects to the pads to enable the transfer of power around the edges of the chip. Additionally, power straps are integrated to deliver power to the center of the chip through the use of higher metal layers, which minimizes issues related to IR drop and electro-migration.

run_floorplanTwo parameters are of importance:

Utilisation Factor = Area occupied by netlist

__________________________

Total area of core

Aspect Ratio = Height

________

Width

A Utilisation Factor of 1 signifies 100% utilisation leaving no space for extra cells such as buffer. However, practically, the Utilisation Factor is 0.5-0.6. Likewise, an Aspect ratio of 1 implies that the chip is square shaped. Any value other than 1 implies rectanglular chip.

Post the floorplan run, a .def file will have been created within the results/floorplan directory. To view the floorplan, Magic is invoked after moving to the results/floorplan directory:

magic -T /home/gagana/OpenLane/pdks/sky130A/libs.tech/magic/sky130A.tech lef read ../../tmp/merged.max.lef def read femto.def

- Zoom in (z)

- Zoom out (shift + z)

- Full view (v)

- Select region (s)

Various components can be identified by selecting and typing what in the tkcon window.

The objective of placement is the convergence of overflow value. If overflow value progressively reduces during the placement run it implies that the design will converge and placement will be successful

run_placementPostplacement the layout can be viewed in magic, by invoking Magic in results/placement and running:

magic -T /home/gagana/OpenLane/pdks/sky130A/libs.tech/magic/sky130A.tech lef read ../../tmp/merged.max.lef def read femto.def

layout

Note 2: Power distribution network generation is usually a part of the floorplan step. However, in the openLANE flow, floorplan does not generate PDN. The steps are - floorplan, placement CTS and then PDN

List of commands to be run in a sequential manner to complete the overall flow for RTL to GDSII layout

run_cts

run_routing

write_powered_verilog

set_netlist $::env(routing_logs)/$::env(femto).powered.v

run_magic

run_magic_spice_export

run_magic_drc

run_lvs

run_antenna_check

getcell sky130_vsdinv- Gaganashree (201EC228)

- Priyanka Gawande (201EC250)

Very Helpful source : Timing Closure of OpenSource Designs

Issues in detail with screenshots

Issue #1

config.json file

{

"DESIGN_NAME": "femto",

"VERILOG_FILES": "dir::src/*.v",

"CLOCK_PORT": "clk",

"CLOCK_PERIOD": 10.0,

"DESIGN_IS_CORE": true

}Command:

./flow.tcl -design femto OpenLane Flow: Flow Failed

25-rcx_sta.worst_slack.rpt

metrics.csv

Since we don’t have a hard requirement for clock frequency we can adjust the clock period to eliminate setup violations. Tried setting up the clock time period to 15 ns and it worked!

Setting: "CLOCK_PERIOD": 15.0

Command:

./flow.tcl -design femto OpenLane Flow: Flow Complete with [WARNING] fanout violation

Issue #2 : Configuring the config.json file to remove fanout violation

25-rcx_sta.max.rpt

25-rcx_sta.worst_slack.rpt

OpenLane Flow: max fanout violation count : 91

Setting: "SYNTH_MAX_FANOUT": 50

Issue #3: Flow fails when executing run_routing in interactive flow

Opening logs file